AMD подробно описывает дизайн 3D V-Cache на ISSCC

На этой неделе International Solid-State Circuits Conference проходит сугубо онлайн, и вот время одной из сессий AMD поделилась некоторыми подробностями дизайна своей 3D V-Cache. Интересной частью здесь является общий дизайн 3D V-Cache от AMD, а также то, как он взаимодействует с процессором.

Говорят, что сам чип кэша имеет площадь 36 мм² и напрямую взаимодействует с кэшем L3 с помощью интерфейса Through Silicon Via или TSV. Чтобы все ядра ЦП могли взаимодействовать с 3D V-Cache, AMD реализовала дизайн общей кольцевой шины на уровне L3. Говорят, что весь кеш L3 доступен каждому из ядер, что должно способствовать дальнейшему повышению производительности.

3D V-Cache состоит из нескольких «фрагментов» по 8 МБ, которые имеют интерфейс с 1024 контактами с одним ядром ЦП, всего 8192 соединения между CCX и 3D V-Cache. Это обеспечивает пропускную способность более 2 терабайт в секунду на срез в полнодуплексном режиме. Это должно обеспечить полную скорость L3 для 3D V-Cache, несмотря на то, что он не является интегрированной частью CCX.

Также сообщается, что AMD улучшила конструкцию своего CCX для грядущего Ryzen 7 5800X3D несколькими способами, чтобы попытаться снизить энергопотребление при одновременном повышении тактовой частоты. AMD еще не объявила дату запуска Ryzen 7 5800X3D, но будет интересно посмотреть, сможет ли 3D V-Cache и различные незначительные оптимизации сделать его конкурентоспособным с процессорами Intel Alder Lake до тех пор, пока не появится Zen 4.

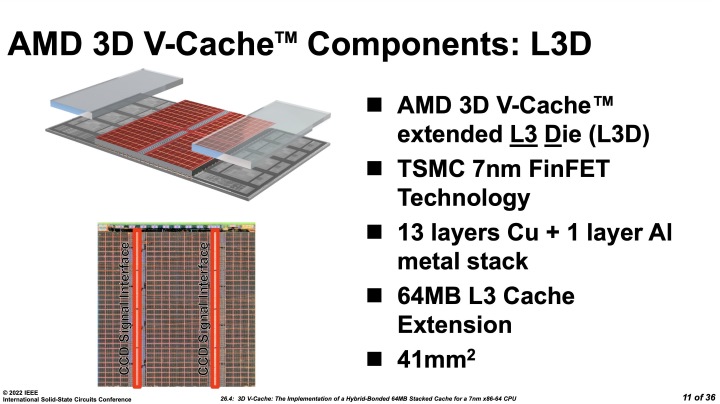

Обновление: в сети появилось ещё несколько слайдов из презентации AMD, которые раскрывают некоторые дополнительные подробности. Прежде всего, SRAM, используемая для 3D V-Cache, производится TSMC на узле N7. AMD называет его «расширенным кристаллом L3» на слайдах, а также расширением кэш L3 на 64 МБ.

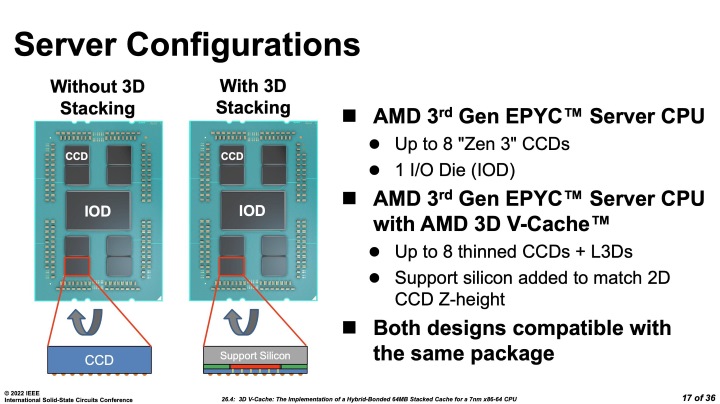

Площадь памяти 3D V-Cache SRAM составляет 41 мм2, а AMD разработала две дополнительные структурные опоры CCD для рассеивания тепла. Чтобы иметь возможность разместить все в той же упаковке, что и процессоры предыдущего поколения, AMD пришлось сделать CCD и кэш L3 тоньше, а структурные опоры также присутствуют для защиты этих утонченных частей за пределами области, охватываемой 3D V-Cache.

Источники: Hardware Luxx, @aschilling