AMD решает проблему нехватки памяти своих MCM-процессоров путем «разложения» северного моста

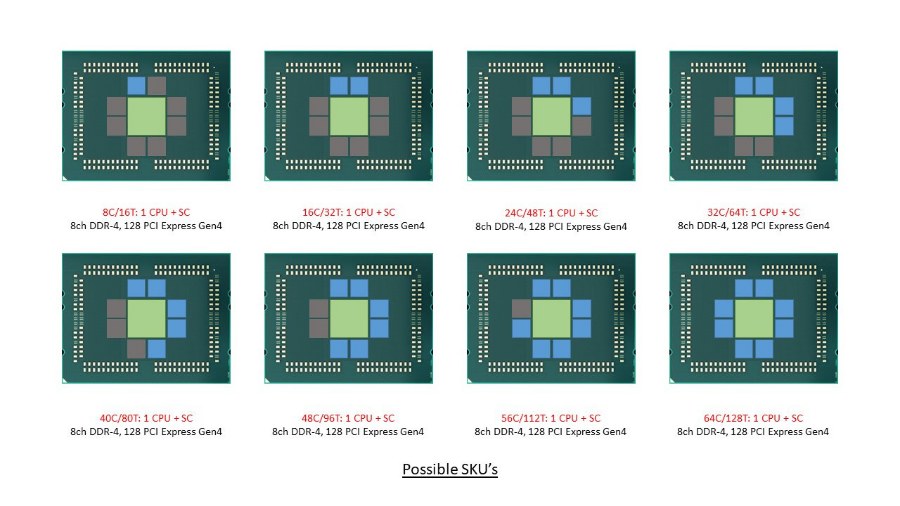

AMD вернулась к конкурентоспособности на рынке центров обработки данных со своими корпоративными процессорами EPYC, представляющие собой многочиповые модули с четырьмя 8-ядерными кристаллами. Каждый кристалл имеет свой собственный интегрированный северный мост, контролирующий 2-канальную память DDR4 и 32-полосный корневой комплексм PCI-Express gen 3.0. В приложениях, которые не только «выбирают» много ядер, но также интенсивно использующих пропускную способность памяти, такой подход к нелокализованной памяти представляется узким местом в дизайне. Семейство Ryzen Threadripper WX проявила многие из этих узких мест, когда тесты кодирования видеоизображения, интенсивно занимающие память, показывают, падение производительности, поскольку кристаллы без прямого доступа к I/O голодают из-за нехватки полосы пропускания памяти. Решение AMD по этой проблеме заключается в разработке процессоров с отключенным северным мостом (часть кристалла с контроллерами памяти и корневым комплексом PCIe). Это решение может быть реализовано в будущих процессорах EPYC 2-го поколения под кодовым названием «Rome».

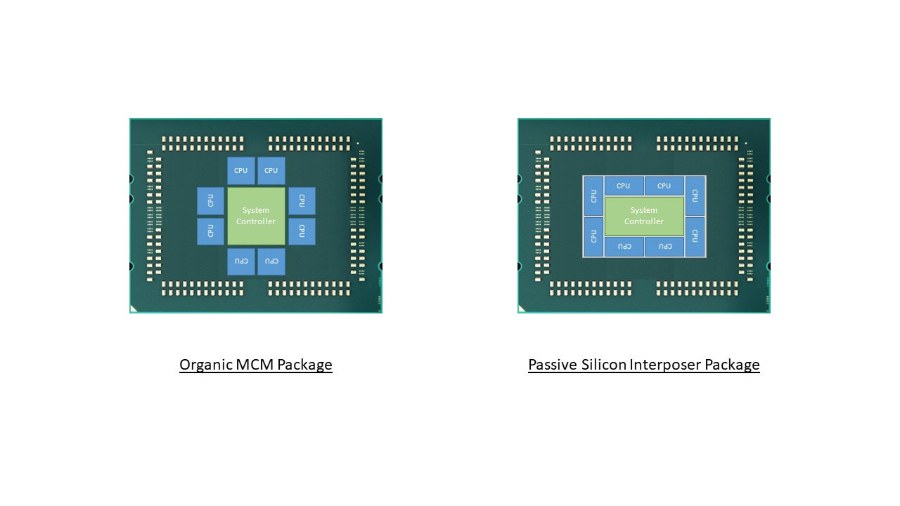

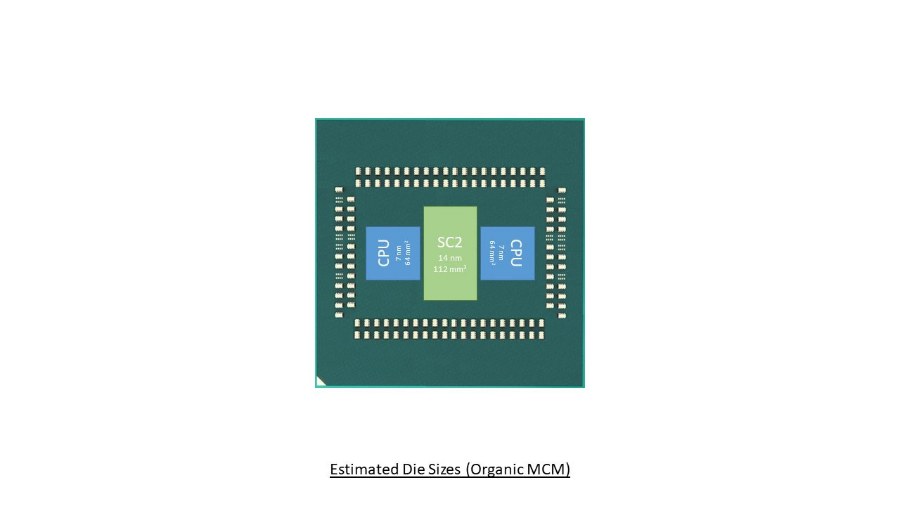

С предстоящим поколением «Zen 2» AMD может разрабатывать процессоры, в которых интегрированный северный мост может быть полностью отключен (так же, как «вычислительные кристаллы» на процессорах Threadripper WX, которые не имеют прямого доступа к памяти и интерфейсу PCIe, и полностью полагаются на InfinityFabric). Эти кристаллы, общаются с внешними вариантами посредством «System Controller», более широкому интерфейсу InfinityFabric. В MCM нового поколения AMD можно будет увидеть централизованный «System Controller», окружённый процессорами, которые могли бы находиться на кремниевом промежуточном устройстве, такого же типа, что и на графических процессорах Vega 10 и Fiji. Подложка представляет собой кремниевую матрицу, облегчающая микроскопическую проводку высокой плотности между кристаллами в MCM. Эти взрывоопасные спекулятивные детали и многое другое были представлены сингапурцем @chiakokhua, The Retired Engineer, отставным инженером VLSI, который сам и рисовал блок-диаграммы.

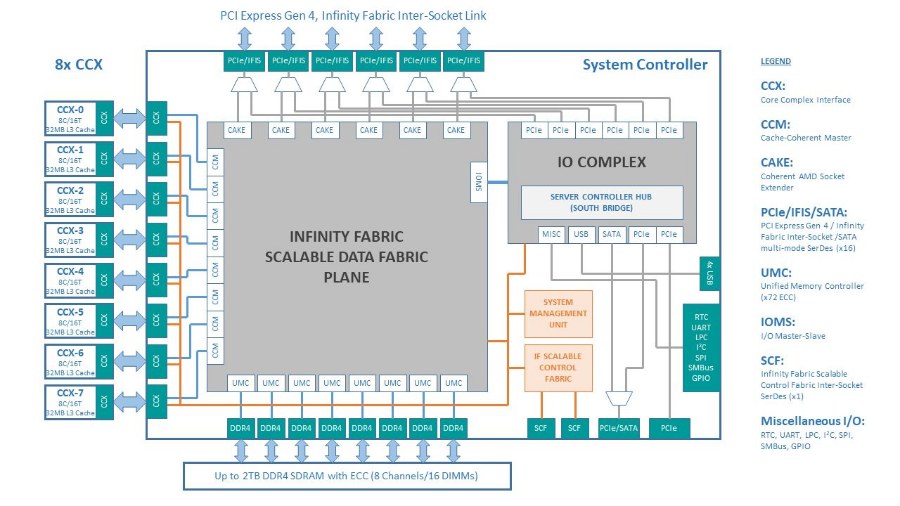

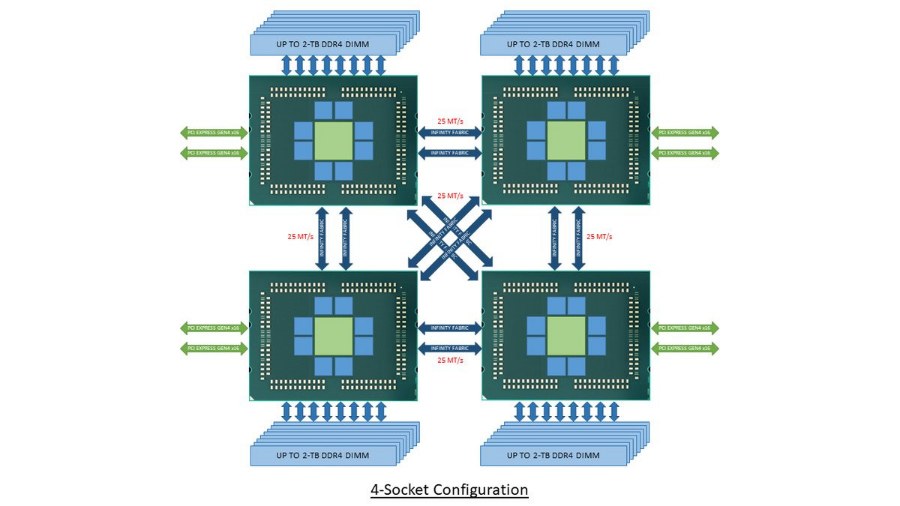

«System Controller» служит городским кварталом для всего процессора и содержит монолитный 8-канальный контроллер памяти DDR4, который может адресовать до 2 ТБ памяти ECC. В отличие от современных процессоров EPYC, этот интерфейс памяти действительно монолитный, то есть, как и реализация Intel. «Системный контроллер» также оснащён корневым комплексом PCI-Express gen 4.0 x96, который может принимать до шести видеокарт с пропускной способностью x16 или до двенадцати на x8. Кроме того, матрица объединяет южный мост, известный как Server Controller Hub, который выделяет общие интерфейсы I/O, такие как SATA, USB и другие устаревшие I/O с низкой пропускной способностью, в дополнение к некоторым каналам PCIe. На платформе всё ещё может оказаться внешний «чипсет», обеспечивающий большую возможность подключений.

Отставной инженер продолжает рассуждать о том, что AMD может даже разрабатывать подобные продукты под сокета AM4 в качестве MCM из двух процессорных кристаллов, совместно использующих системный контроллер; но предупредил, что это маловероятно. Учитывая, что клиентский сегмент имеет низкую маржу по сравнению с предприятиями, и AMD захочет создавать продукты лишь с одним кристаллом — те, в которых интегрированный северный мост не отключен. Тем не менее, это не полностью исключает возможность использования MCM с 2-мя кристаллами для «высокоуровневых» SKU, которые AMD может продавать по цене около 500 $. В таких случаях системный контроллер может быть более компактным, с меньшим количеством ссылок InfinityFabric, двухканальной памятью I/O и 32-полосным слотом PCIe gen 4.0.

AMD планирует представить MCM «Rome» в 2018 году.